Engineered Crystals Could Help Computers Run on Less Power

Computers may be growing smaller and more powerful, but they require a great deal of energy to operate. The total amount of energy the U.S. dedicates to computing has risen dramatically over the last decade and is quickly approaching that of other major sectors, like transportation.

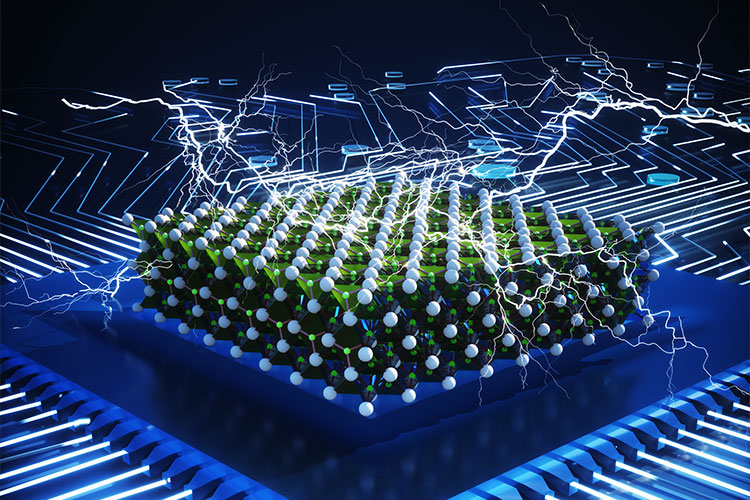

In a study published online this week in the journal Nature, University of California, Berkeley, engineers describe a major breakthrough in the design of a component of transistors — the tiny electrical switches that form the building blocks of computers — that could significantly reduce their energy consumption without sacrificing speed, size or performance. The component, called the gate oxide, plays a key role in switching the transistor on and off.

“We have been able to show that our gate-oxide technology is better than commercially available transistors: What the trillion-dollar semiconductor industry can do today — we can essentially beat them,” said study senior author Sayeef Salahuddin, the TSMC Distinguished professor of Electrical Engineering and Computer Sciences at UC Berkeley.

This boost in efficiency is made possible by an effect called negative capacitance, which helps reduce the amount of voltage that is needed to store charge in a material. Salahuddin theoretically predicted the existence of negative capacitance in 2008 and first demonstrated the effect in a ferroelectric crystal in 2011.

The new study shows how negative capacitance can be achieved in an engineered crystal composed of a layered stack of hafnium oxide and zirconium oxide, which is readily compatible with advanced silicon transistors. By incorporating the material into model transistors, the study demonstrates how the negative capacitance effect can significantly lower the amount of voltage required to control transistors, and as a result, the amount of energy consumed by a computer.

“In the last 10 years, the energy used for computing has increased exponentially, already accounting for single digit percentages of the world’s energy production, which grows only linearly, without an end in sight,” Salahuddin said. “Usually, when we are using our computers and our cell phones, we don’t think about how much energy we are using. But it is a huge amount, and it is only going to go up. Our goal is to reduce the energy needs of this basic building block of computing, because that brings down the energy needs for the entire system.”

Bringing negative capacitance to real technology

State-of-the-art laptops and smart phones contain tens of billions of tiny silicon transistors, and each of which must be controlled by applying a voltage. The gate oxide is a thin layer of material that converts the applied voltage into an electric charge, which then switches the transistor.

Negative capacitance can boost the performance of the gate oxide by reducing the amount of voltage required to achieve a given electrical charge. But the effect can’t be achieved in just any material. Creating negative capacitance requires careful manipulation of a material property called ferroelectricity, which occurs when a material exhibits a spontaneous electrical field. Previously, the effect has only been achieved in ferroelectric materials called perovskites, whose crystal structure is not compatible with silicon.

In the study, the team showed that negative capacitance can also be achieved by combining hafnium oxide and zirconium oxide in an engineered crystal structure called a superlattice, which leads to simultaneous ferroelectricity and antiferroelectricity.

“We found that this combination actually gives us an even better negative capacitance effect, which shows that this negative capacitance phenomena is a lot broader than originally thought,” said study co-first author Suraj Cheema, a postdoctoral researcher at UC Berkeley. “Negative capacitance doesn’t just occur in the conventional picture of a ferroelectric with a dielectric, which is what’s been studied over the past decade. You can actually make the effect even stronger by engineering these crystal structures to exploit antiferroelectricity in tandem with ferroelectricity.”

The researchers found that a superlattice structure composed of three atomic layers of zirconium oxide sandwiched between two single atomic layers of hafnium oxide, totaling less than two nanometers in thickness, provided the best negative capacitance effect. Because most state-of-the-art silicon transistors already use a 2-nanometer gate oxide composed of hafnium oxide on top of silicon dioxide, and since zirconium oxide is also used in silicon technologies, these superlattice structures can easily be integrated into advanced transistors.

To test how well the superlattice structure would perform as a gate oxide, the team fabricated short channel transistors and tested their capabilities. These transistors would require approximately 30% less voltage while maintaining semiconductor industry benchmarks and with no loss of reliability, compared to existing transistors.

“One of the issues that we often see in this type of research is that we can we can demonstrate various phenomena in materials, but those materials are not compatible with advanced computing materials, and so we cannot bring the benefit to real technology,” Salahuddin said. “This work transforms negative capacitance from an academic topic to something that could actually be used in an advanced transistor.”

Nirmaan Shanker of UC Berkeley is also a co-first author of this study. Additional co-authors include Li-Chen Wang, Cheng-Hsiang Hsu, Shang-Lin Hsu, Yu-Hung Liao, Wenshen Li, Jong-Ho Bae, Steve K. Volkman, Daewoong Kwon, Yoonsoo Rho, Costas P. Grigoropoulos, Ramamoorthy Ramesh and Chenming Hu of UC Berkeley; Matthew San Jose, Jorge Gomez, Wriddhi Chakraborty, Patrick Fay and Suman Datta of the University of Notre Dame; Gianni Pinelli, Ravi Rastogi, Dominick Pipitone, Corey Stull, Matthew Cook, Brian Tyrrell and Mohamed Mohamed of the Massachusetts Institute of Technology’s Lincoln Laboratory; Vladimir A. Stoica of Pennsylvania State University; Zhan Zhang and John W. Freeland of Argonne National Laboratory; Christopher J. Tassone and Apurva Mehta of SLAC National Accelerator Laboratory; Ghazal Saheli and David Thompson of Applied Materials; Dong Ik Suh and Won-Tae Koo of SK Hynix; Kab-Jin Nam, Dong Jin Jung, Woo-Bin Song, Seunggeol Nam and Jinseong Heo of Samsung Electronics; Chung-Hsun Lin of Intel Corporation; Narendra Pariha and Souvik Mahapatra of the Indian Institute of Technology; and Padraic Shafer and Jim Ciston of Lawrence Berkeley National Laboratory.

This research was supported in part by the Berkeley Center for Negative Capacitance Transistors (BCNCT), the DARPA Technologies for Mixed-mode Ultra Scaled Integrated Circuits (T-MUSIC) program, the University of California Multicampus Research Programs and Initiatives (UC MRPI) project and the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division under contract No. DE-AC02-05-CH11231 (Microelectronics Co-Design program).